NVIDIA “đốt nóng” cuộc đua HBM4: Các ông lớn bộ nhớ tăng tốc lên 16 lớp

Tại CES 2026, NVIDIA với chip Rubin đã đẩy chuẩn HBM4 vượt mốc 11 Gbps, buộc SK hynix, Samsung và Micron phải điều chỉnh thiết kế và tăng tốc phát triển HBM4 16 lớp. Theo TrendForce, HBM4 khó có thể sản xuất hàng loạt trước cuối quý I/2026. Đây là thời điểm phù hợp để điểm lại các “đại gia” bộ nhớ cùng những lợi thế HBM4 và thách thức phía trước.

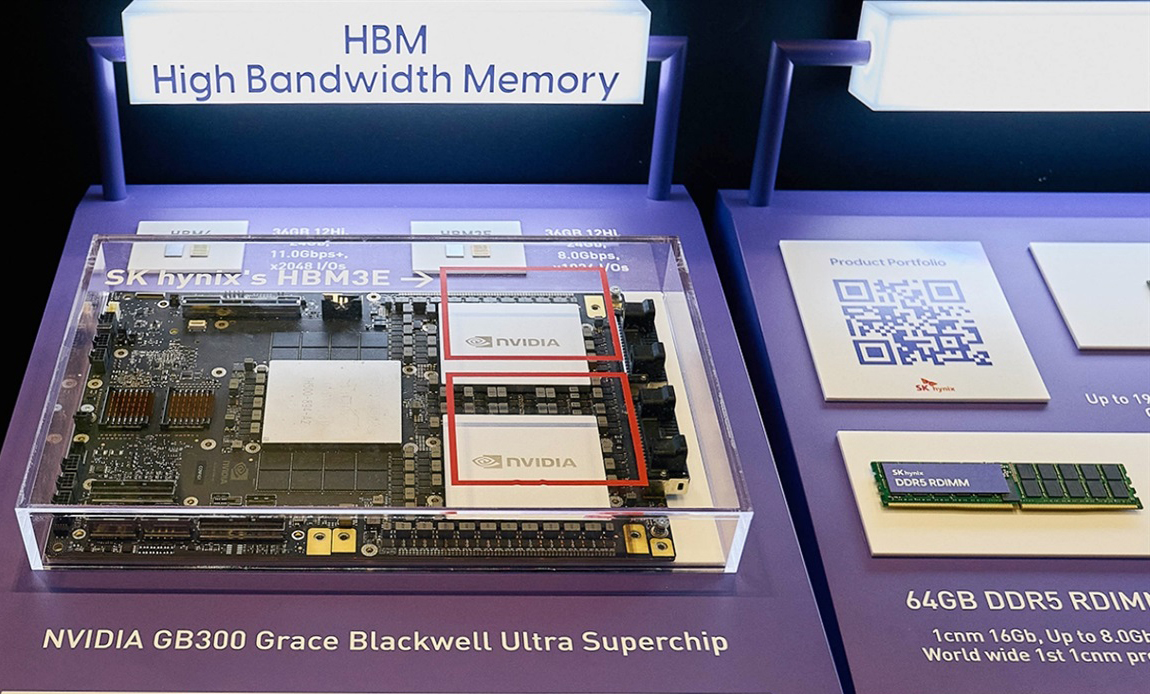

SK hynix tăng tốc HBM4 16 lớp, đi trước cả giai đoạn tăng sản lượng 12 lớp

Là đơn vị dẫn đầu HBM hiện tại, SK hynix đã gây chú ý khi trình diễn HBM4 16 lớp tại CES, trở thành công ty đầu tiên làm được điều này. Theo Etnews, HBM4 16 lớp, dung lượng 48 GB được phát triển dựa trên mẫu 12 lớp, 36 GB vốn đã lập kỷ lục tốc độ 11,7 Gbps. Việc xếp chồng DRAM lên tới 16 lớp giúp SK hynix tăng mạnh cả dung lượng lẫn tốc độ, đạt băng thông vượt 2 TB/s.

Tuy nhiên, The Korea Herald cho biết việc mở rộng từ 12 lên 16 lớp khó hơn nhiều so với từ 8 lên 12. Các nhà phân tích ước tính HBM 16 lớp yêu cầu wafer mỏng khoảng 30 µm, so với ~50 µm ở thiết kế 12 lớp hiện nay. Trong bối cảnh JEDEC giới hạn chiều cao gói HBM4 ở mức 775 µm, các phương pháp truyền thống gần như không còn dư địa mở rộng, làm nổi bật rào cản kỹ thuật phía trước.

Trong khi ngành ngày càng xem hybrid bonding là lời giải dài hạn, SK hynix hiện dẫn đầu bằng cách ổn định tỷ lệ thành phẩm (yield) với quy trình MR-MUF (Mass Reflow Molded Underfill). Ngược lại, Samsung và Micron vẫn dựa vào TC-NCF (Thermal Compression với Non-Conductive Film).

Theo SK hynix, MR-MUF gia nhiệt và kết nối toàn bộ các chip xếp chồng theo chiều dọc trong một lần, hiệu quả hơn TC-NCF – vốn phải phủ vật liệu dạng film sau mỗi lớp chip. Do chip DRAM trong HBM3 12 lớp phải mỏng hơn khoảng 40% so với HBM3 8 lớp để đảm bảo chiều cao tổng thể, hiện tượng cong vênh chip trở thành vấn đề lớn. Để khắc phục, SK hynix đã đưa vào vật liệu EMC mới trong quy trình MR-MUF nâng cao, giúp cải thiện tản nhiệt khoảng 1,6 lần so với phiên bản ban đầu.

TechNews nhận định rằng dù SK hynix cũng phát triển hybrid bonding như phương án dự phòng, chiến lược cốt lõi của hãng vẫn là kéo dài vòng đời công nghệ MR-MUF dẫn đầu ngành càng lâu càng tốt.

Samsung dẫn trước nhờ DRAM 1c; hybrid bonding được đưa vào cuộc chơi

Ở chiều ngược lại, TrendForce cho biết Samsung đang có lợi thế sớm khi áp dụng tiến trình 1c nm (10nm-class, thế hệ thứ 6) cho HBM4 và sử dụng công nghệ foundry nội bộ tiên tiến cho base die. Cách tiếp cận này được kỳ vọng mang lại tốc độ truyền cao hơn, giúp Samsung có khả năng đạt chứng nhận sớm nhất và giành lợi thế trong việc cung ứng các sản phẩm Rubin cao cấp.

Theo Chosun Biz, Samsung đã áp dụng tiến trình logic 4nm cho HBM4 dựa trên DRAM 1c và tinh chỉnh thiết kế để đạt tốc độ vượt 11 Gbps, cao hơn yêu cầu của khách hàng. Trước đó, Etnews đưa tin khi các đối thủ xây dựng HBM4 trên node DRAM 1b cũ hơn, Samsung đã “đổi luật chơi” bằng việc chuyển sang 1c. Hiện hãng đã bắt đầu sản xuất DRAM 1c, với tỷ lệ yield tiến gần mục tiêu 80% cho sản xuất hàng loạt.

Đáng chú ý, Sisa Journal cho biết trong khi SK hynix tiếp tục trung thành với MR-MUF cho HBM 16 lớp, Samsung đang tăng tốc hybrid bonding, nhắm tới HBM4E 16 lớp vào năm 2028. Tuy nhiên, dù Samsung đã cung cấp mẫu HBM4 hybrid-bonded cho các khách hàng chủ chốt, bao gồm NVIDIA, tỷ lệ yield hiện chỉ khoảng 10%.

Với năng lực sản xuất phân bổ đồng đều nhất, Samsung không chỉ dựa vào công nghệ. Trước nhu cầu mạnh, Etnews cho biết hãng lên kế hoạch tăng sản lượng HBM thêm 50% trong năm 2026, đạt khoảng 250.000 wafer/tháng vào cuối năm, tập trung chủ yếu cho HBM4.

Micron tăng tốc mở rộng công suất

Micron, sản xuất HBM4 trên node 1 beta, cho biết trong cuộc họp công bố kết quả kinh doanh tháng 12 rằng sản phẩm đạt tốc độ dẫn đầu ngành trên 11 Gbps và đang đi đúng lộ trình tăng sản lượng với yield cao trong quý II/2026. Công ty nhấn mạnh cả base logic và DRAM core die đều được thiết kế và sản xuất nội bộ bằng các công nghệ CMOS và kim loại hóa tiên tiến.

Dù thông tin chi tiết về HBM4 của Micron còn hạn chế, Etnews cho biết hãng đang tận dụng thế mạnh HBM tiêu thụ điện năng thấp để thách thức các đối thủ Hàn Quốc bằng cách khóa chặt thêm công suất sản xuất. Micron đang đẩy nhanh từ HBM4 12 lớp lên 16 lớp, đồng thời mở rộng hiện diện thị trường.

New Daily, dẫn lời CEO Sanjay Mehrotra, cho biết nhà máy đóng gói tiên tiến tại Singapore sắp tới và cơ sở Hiroshima (Nhật Bản) được kỳ vọng sẽ giảm đáng kể nút thắt công suất.

Cuộc đua HBM4 đang nóng lên với tốc độ chưa từng có. Khi HBM4 12 lớp còn chưa tăng sản lượng hoàn toàn, yêu cầu của NVIDIA về nguồn cung 16 lớp trong nửa cuối năm 2026 đã đặt các “ông lớn” bộ nhớ vào tình trạng báo động cao, theo Etnews.

Ở thời điểm hiện tại, SK hynix dẫn đầu với MR-MUF hoàn thiện và các màn trình diễn 16 lớp sớm; Samsung thúc đẩy DRAM 1c và hybrid bonding để bứt phá; còn Micron mở rộng công suất để thu hẹp khoảng cách. Doanh nghiệp đầu tiên vượt qua rào cản công nghệ của xếp chồng 16 lớp không chỉ đáp ứng cơn khát AI đang tăng vọt, mà còn có cơ hội giành ngôi vương thế hệ tiếp theo, mở màn cho cuộc đối đầu khốc liệt trong kỷ nguyên HBM4.

Chia sẻ bài viết

Bình luận

( 0 bình luận )Bình luận của bạn

Tin tức liên quan